Seitenkanäle sind keine Entdeckung des Informationszeitalters. Sie existieren seit Anbeginn der Menschheit.

Was genau sind Seitenkanäle?

Seitenkanäle sind ein Phänomen der Kommunikation, und das nicht nur im technischen Kontext. Man unterscheidet sie vom direkten Kommunikationskanal, den ein Sender und Empfänger miteinander führen, um Informationen auszutauschen.

Zur Veranschaulichung stelle man sich vor, dass zwei Personen einen Termin verabreden. Die eine Person schlägt eine Uhrzeit vor und fragt, ob diese der anderen Person passe. Obwohl letztere bejaht, bemerkt erstere, dass das nicht stimmen kann. Die Körpersprache der anderen Person verriet, dass die Uhrzeit eigentlich nicht passt. Die Körpersprache – ein Seitenkanal – gehört, wie das gesprochene Wort, zur menschlichen Kommunikation dazu. Das System Mensch kann nicht anders.

Auf technische Informationssysteme trifft dasselbe zu. In der Regel verbindet ein Datenkanal, der direkte Kommunikationskanal, ein Informationssystem mit einem anderen. Aber auch hier gibt es eine Art Körpersprache, die letzendes auf die Technologie und den Strombedarf zurückzuführen ist. Die Herzstücke dieser Informationssysteme, in der Regel die Prozessoren oder auch CPUs, basieren auf einem wichtigen Halbleiterprozess, der sogenannten CMOS-Technik. Prozessoren in dieser Technik verändern ihren Strombedarf in Abhängigkeit der Bits, die in den Informationen und Daten stecken. Dieser veränderliche Strombedarf – ein Seitenkanal – lässt sich messen und somit auch indirekt die Daten. Das Informationssystem kann nicht anders.

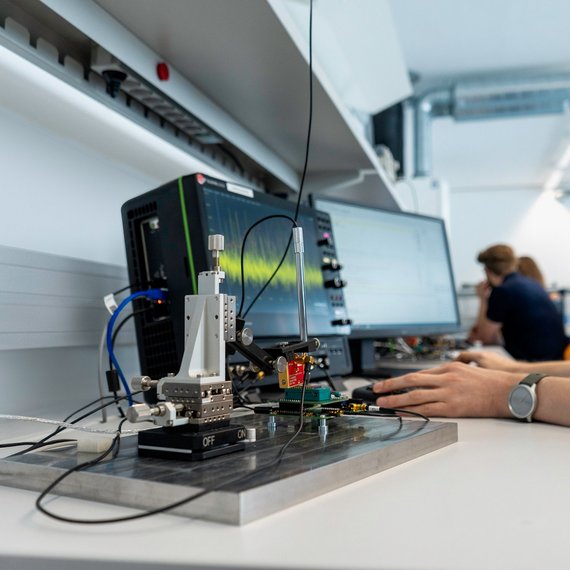

Halbleiter Chips für den IT-Security Bereich bilden hier selbstverständlich keine Ausnahme. Deshalb messen wir in unserem Hardwarelabor, diesen veränderlichen Strombedarf, genau dann, wenn ein Security Chip geheime Daten verarbeitet und prüfen, ob ein Zusammenhang zwischen diesen beiden besteht. An dieser Stelle ist es einfach, besteht ein Zusammenhang ist der Chip durchgefallen, ein erheblicher Mangel sozusagen. Wenn nicht, dann besteht der Chip die „TÜV-Prüfung“. Der Chiphersteller muss nachbessern und den Chip erneut zur Prüfung vorlegen.